# Identifying the Electronic and Ionic Transport in Area-Dependent VCM

"Allowing engineering and simulation of memristive devices for neurmorphic circuits"

C. Wittberg<sup>1</sup>, D. Spithouris<sup>1</sup>, J. Hellwig<sup>1</sup>, R. Dittmann<sup>1</sup>

<sup>1</sup>Peter-Grünberg-Institute (PGI-7), Forschungszentrum Jülich, Germany

#### Motivation: Gradual Area-Dependent memristive devices are needed for analog computing and neuromorphic applications<sup>1</sup>

| Feature                                    | Gradual, Area-Dependent<br>Switching       | Binary / Abrupt Filamentary<br>Switching                                  |

|--------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------|

| Synaptic<br>Behavior                       | Analog (continuous weight tuning)          | Digital (discrete on/off states)                                          |

| Learning<br>Performance                    | High precision and stable convergence      | Poor convergence and limited learning accuracy                            |

| Variability                                | Inherently low due to homogenous switching | High due to random nature of filament formation                           |

| Update<br>Control                          | Fine, incremental conductance changes      | Sudden, large conductance jumps                                           |

| Suitability for<br>Neuromorphic<br>Systems | ✓ Ideal — mimics biological synapses       | Limited — too discrete for analog learning. Good for memory applications. |

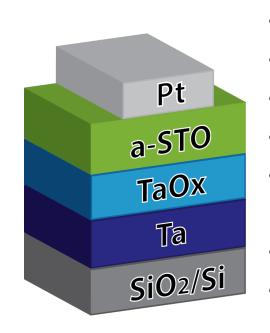

#### Model system: Area-dependent volatile a-STO based VCM devices

- Area-dependent 8-wise switching.

- Gradual switching.

- CMOS BEOL compatible fabrication process.

- Very low variability.

- Self-rectifying, current compliance-free operation.

- Great endurance >5 · 10<sup>6</sup> cycles

- Volatile behavior with tunable retention times (milliseconds to several seconds), enabling the emulation of short-term plasticity (STP) in neuromorphic circuits.

Good physical understanding of these type of devices for device engineering and circuit simulations.

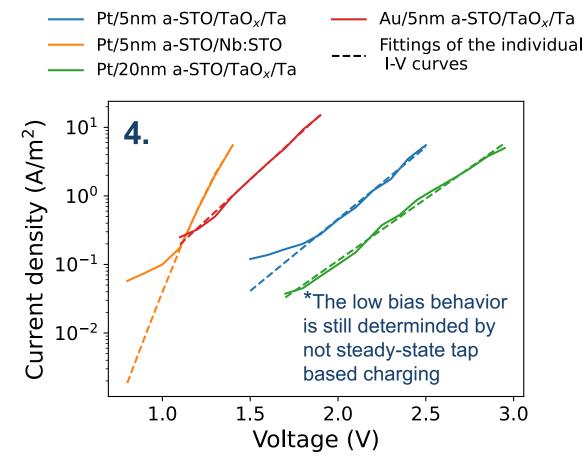

## Electronic Model: Understanding the electron transport through heterostructure

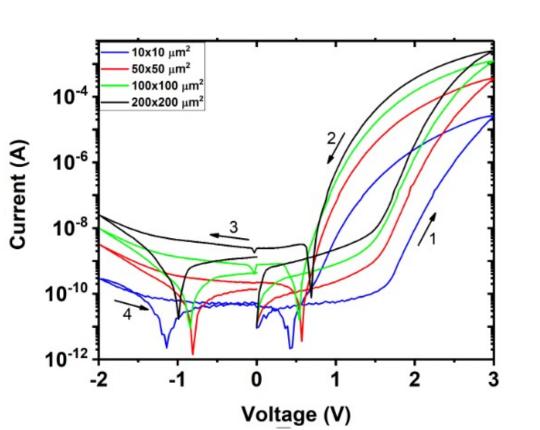

#### Band diagram and possible conduction mechanisms

- Conduction band minimum (CBM) including all the potential conduction-limiting transport mechanisms.

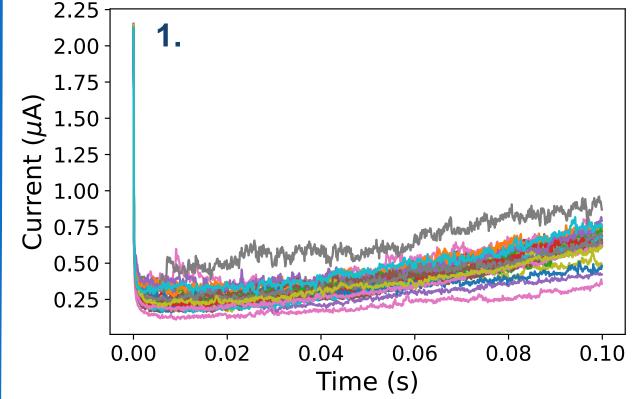

- 2. Estimation of the current density through the TaO<sub>x</sub> barrier with a newly presented trap assisted tunneling (TAT) model shows that the TaO<sub>x</sub> barrier is not current limiting

- Standard transport analysis shows tunneling through Pt/a-STO barrier is current-limiting but cannot explain the observed behavior.

- 4. Model fittings fail to match both switching and tranport measurements

No here considered transport mechanism can explain the measured current-voltage relation with realistic parameter

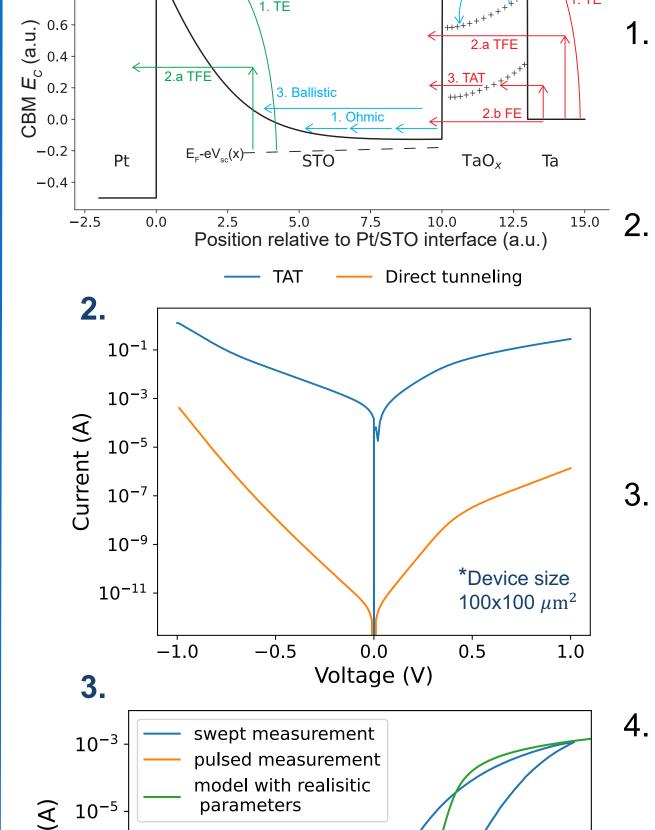

#### Consideration trap based electron exchange effects

The standard measurement and fitting approach does not work for transport study

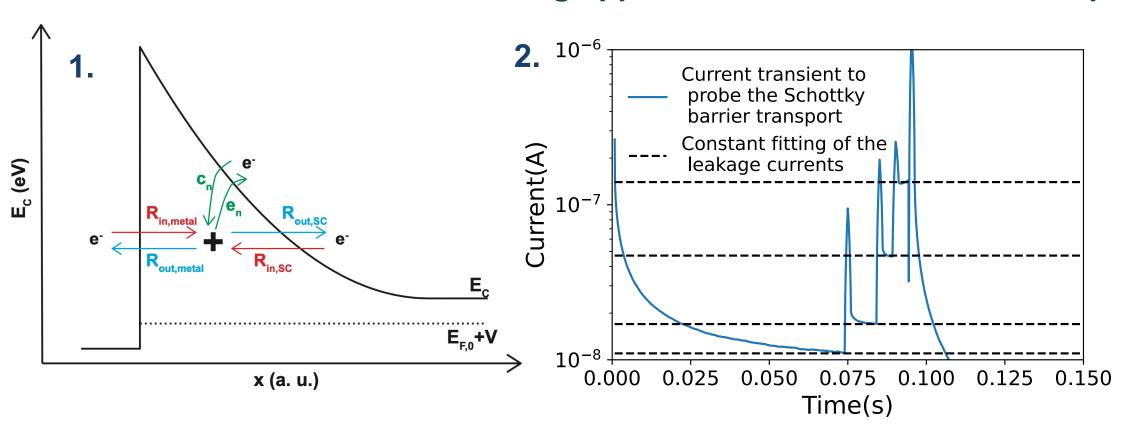

. Schematic representation of electron trap exchange mechanisms via tunneling or thermal exchange. The ionized trap density follows the differential equation:

$$\frac{dD_t(x,\phi_t,t)}{dt} = \frac{1}{d\phi_t} \left( R_{out,SC} + R_{out,metal} + e_n - R_{in,SC} - R_{in,metal} - c_n \right)$$

- 2. Time dependent current response of electron trap exchange dynamics and corresponding steady-state current under a sequence of increasing applied biases

- ⇒Accurate steady-state I-V data can only be obtained by this method

- 3. Under steady-state conditions, the electron concentration controlled by trap exchange can be represented by the voltage dependent quasi-Fermi level determining electron transport through the Schottky barrier.

- 4. Only Tsu-Esaki tunneling conduction including the shape of the quasi Fermi level can describe the I-V relation

## Ionic model: Understanding switching based on Oxygen vacancy migration

#### Semi-analytical ion migration model

Voltage (V)

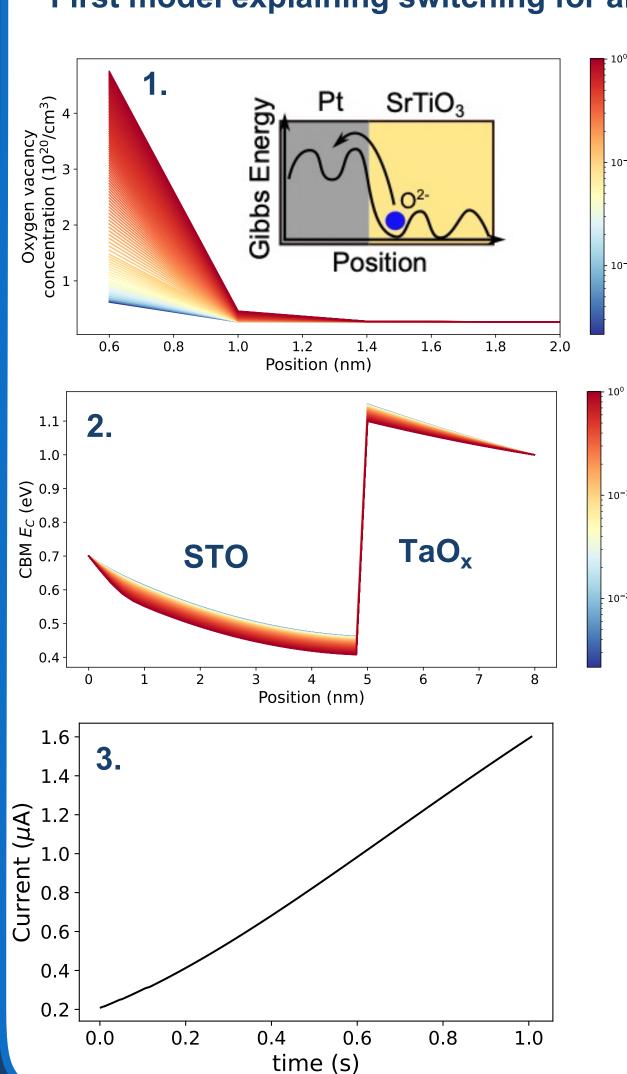

First model explaining switching for all type 1 memristive devices

[1] D. V Christensen et al., Neuromorph. Comput. Eng. 2, 022501, 2022.

[2] J. Hellwig et al., Adv. Electron. Mater. 10.12, 2400062, 2024

[3] S. Menzel et al., Adv. Funct. Mater. 21, 4487-4492, 2011

[4] D. Cooper et al., Adv. Mater. 29, 1700212, 2017

\*Device size  $100 \times 100 \ \mu \text{m}^2$

- We developed a rigorous ion migration model through the Gibbs Free energy by solving a system of differential equations<sup>2,3</sup>.

- Time dependent Oxygen vacancy concentration under an applied forward bias, showing Oxygen being extracted at the Pt/a-STO interface<sup>4</sup>.

- Modulation of the CBM with time due to the increased oxygen vacancy concentration. The **TaO**<sub>x</sub> acts as a protective layer limiting the electric field in the a-STO.

- 3. The modulation of the Pt/a-STO barrier leads to a modulation of the tunneling current and switching.

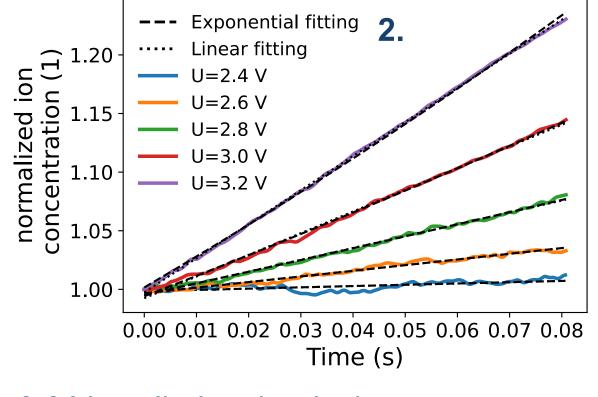

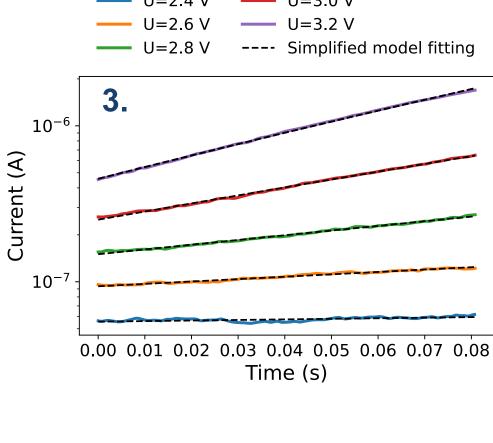

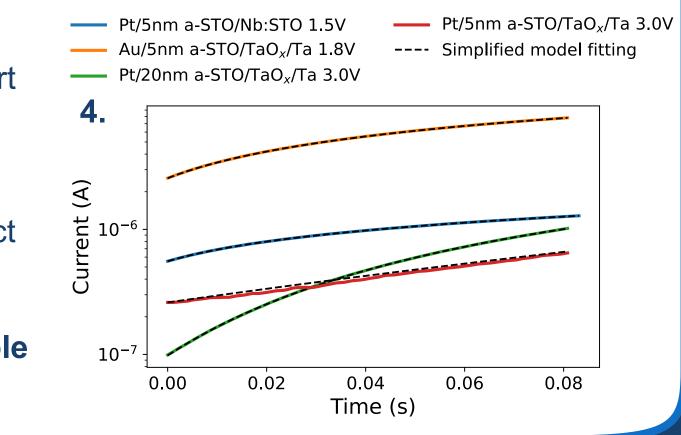

### Simplified model for fitting the measured switching behavior

- Measured switching I-t transients for U=3.0 V applied to the device.

- 2. Using averaged switching transients and the quasi-Fermi-based transport model, we determine the trap concentration via a simplified single-rate switching fit.

- 3. The fitted concentration and quasi-Fermi including transport model predict the I-t switching transient, enabling comparison with measurements.

- 4. The I-t switching transients match the measurements with reasonable parameters ⇒ Models are accurate

#### **Summary and Outlook:**

- Explained the electron transport by including the shape of the quasi–Fermi level being determined by trap based electron exchange effects.

- Explained switching by the first rigorous ion migration model also applicable for type 1 memristive devices.

- The model allows insights into the accurate estimation of currents, read-out times and switching times enabling predictions of the device performance and compact modeling.

- It also provides insights into device functionality and parameter extraction for material and device optimization.